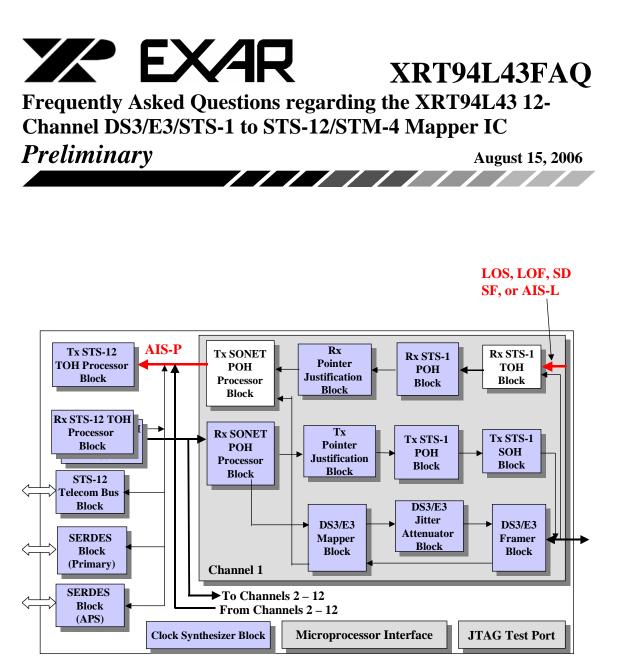

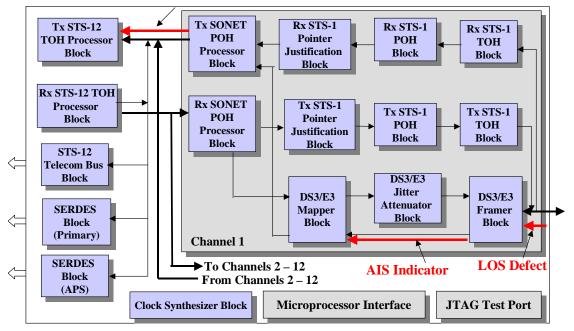

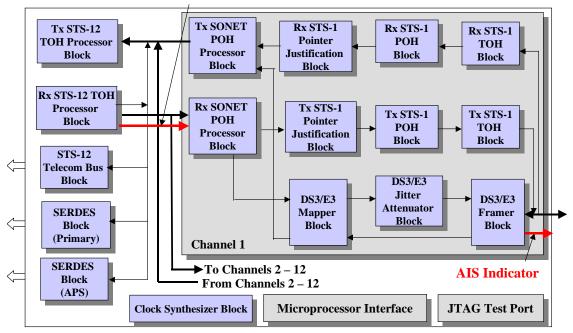

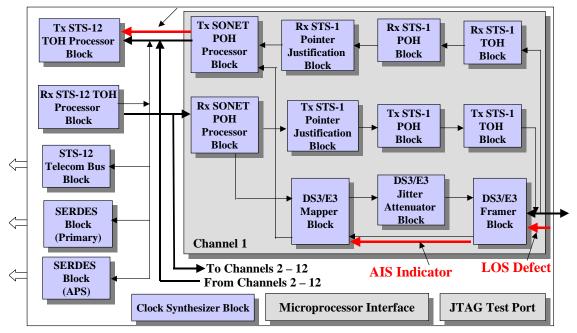

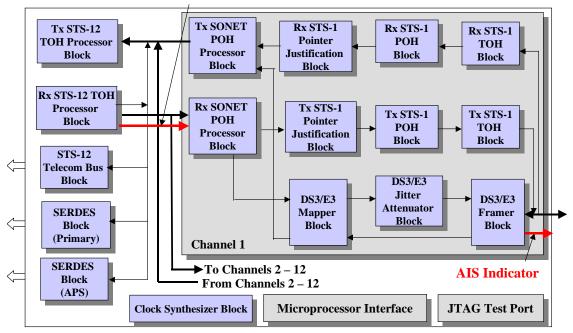

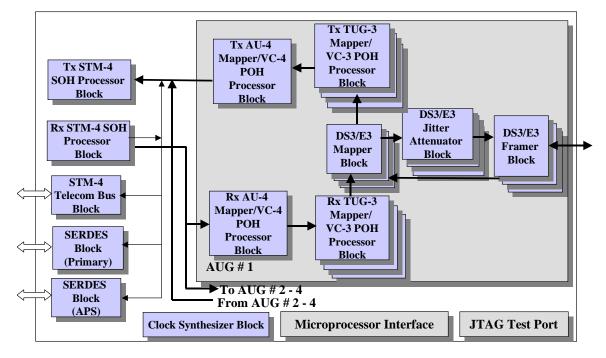

## FREQUENTLY ASKED QUESTIONS REGARDING THE 12-CHANNEL DS3/E3/STS-1 TO STS-12/STM-4 MAPPER IC

##

Frequently Asked Questions regarding the XRT94L43 12-Channel DS3/E3/STS-1 to STS-12/STM-4 Mapper IC

#### **Preliminary**

August 15, 2006

XRT94L43FAQ

####

#### Table of Contents

| Table of Contents   2                                                               |

|-------------------------------------------------------------------------------------|

| Q1: On-Chip Jitter Attenuator-related Questions                                     |

| Q1.1: What is APS Recovery Time of the XRT94L43 device?                             |

| Q1.2: What Frequency Accuracy is required at the REFCLK34 (pin P23), REFCLK45       |

| (pin P25) or REFCLK51 (pin P24) input pins?                                         |

| Q1.3: If one only intends to support DS3 and STS-1/STM-0 signals via the            |

| XRT94L43 device, is it still necessary to supply a 34.368MHz clock signal to the    |

| REFCLK34 input pin?                                                                 |

| Q1.4: If one only intends to support DS3 and E3 signals via the XRT94L43 device, is |

| it still necessary to supply a 51.84MHz clock signal to the REFCLK51 input pin? 10  |

| Q1.5: Are the DS3 signals, which are extracted out of the XRT94L43 device (from     |

| SONET) capable of complying with the Category 1 Intrinsic Jitter Requirements per   |

| Telcordia GR-253-CORE and ANSI T1.105.03-1994?                                      |

| Q1.6: What does one need to do in order to configure the XRT94L43 Device to         |

| support "Daisy-Chain" Testing?                                                      |

| Q2: Clock Synthesizer Block-Related Questions                                       |

| Q2.1: What Frequency Accuracy is required at the REFCLK input pin (pin R1)? 13      |

| Q2.2: How does one configure the Clock Synthesizer block to synthesize a 77.76MHz   |

| clock signal, when provided with a 19.44MHz clock signal? 14                        |

| Q2.3 How does one configure the XRT94L43 Device to use the 77.76MHz clock           |

| signal (which is supplied to the REFCLK input pin) as a timing reference? 15        |

| Q3: General Configuration-Related Questions                                         |

| Q3.1 Is it permissible to configure the XRT94L43 device to support combinations of  |

| the STS-3 Telecom Bus Interface and the DS3/E3/STS-1 Interface? 16                  |

| Q3.2 How does one configure a given channel to operate in the DS3/E3 Framer         |

| Mode?                                                                               |

| Q3.3 How does one configure a given channel to operate in the STS-1 Mode?           |

| Q3.4: What type of Loop-back Modes are available within the XRT94L43 device? 24     |

| Q3.5: How does one configure the XRT94L43 device to operate in the "Remote Line     |

| Loop-back" Mode?                                                                    |

| Q3.6: How does one configure the XRT94L43 device to operate in the "Local           |

| Transport Loop-back" Mode?                                                          |

| Q3.7: How does one configure the XRT94L43 device to operate in the "Local Path      |

| Loop-back" Mode?                                                                    |

| Q3.8: How does one configure a given channel, within the XRT94L43 device to         |

| operate in the "STS-1 Local Loop-back" Mode?                                        |

##

Frequently Asked Questions regarding the XRT94L43 12-Channel DS3/E3/STS-1 to STS-12/STM-4 Mapper IC

#### **Preliminary**

August 15, 2006

XRT94L43FAQ

|   | Q3.9: How does one configure a given channel, within the XRT94L43 device to operate in the "STS-1 Remote Loop-back" Mode?                                                                                                                           |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | Q3.10: How does one configure a given channel, (within the DS3/E3 Framer block) of the XRT94L43 device to operate in the "DS3/E3 Framer Local Loop-back" Mode? 42 Q3.11: How does one configure a given channel (within the DS3/E3 Framer block) of |

|   | the XRT94L43 device to operate in the "DS3/E3 Framer Remote Loop-back" Mode?                                                                                                                                                                        |

|   | Q3.12: If the XRT94L43 Device has been configured to operate in the SDH Mode,                                                                                                                                                                       |

|   | can be configured to support the AU-3/VC-3 and the AU-4/TUG-3 Mapper Modes? 46 Q3.13: Does the XRT94L43 device contain any BERT (Bit Error Rate Test)                                                                                               |

|   | capability?                                                                                                                                                                                                                                         |

|   | signal?                                                                                                                                                                                                                                             |

|   | Q3.15: How are the individual DS3 and E3 Channels mapped into an STM-4/TUG-3                                                                                                                                                                        |

|   | signal?                                                                                                                                                                                                                                             |

| Q | 4: Automatic Protection Switching (APS)-related Questions                                                                                                                                                                                           |

|   | Q4.1: What resources does the XRT94L43 device have to support APS?                                                                                                                                                                                  |

|   | Q4.2: What is going on within the XRT94L43 device, when one implements APS?. 63                                                                                                                                                                     |

|   | Q4.3 How does one configure the XRT94L43 device to automatically perform APS in                                                                                                                                                                     |

|   | the event of an LOS condition?                                                                                                                                                                                                                      |

|   | Q4.4 Is there a way to determine whether the XRT94L43 device is processing the incoming STS-12 data that is being applied to the Primary or the Redundant Receive                                                                                   |

|   | STS-12/STM-4 PECL Interface port?                                                                                                                                                                                                                   |

|   | Q4.5: Are both the "Primary" and "Redundant" Transmit PECL Clock and Data                                                                                                                                                                           |

|   | Output signals always active?                                                                                                                                                                                                                       |

|   | Q4.6 If the XRT94L43 device is current processing the incoming STS-12/STM-4                                                                                                                                                                         |

|   | signal that is being applied to the "Primary Receive STS-12/STM-4 PECL Interface"                                                                                                                                                                   |

|   | port, can the XRT94L43 device monitor the state of the STS-12/STM-4 signal that is                                                                                                                                                                  |

|   | being applied to the "Redundant Receive STS-12/STM-4 PECL Interface" port?72                                                                                                                                                                        |

|   | Q4.7: How does one configure the XRT94L43 to perform APS (Automatic Protection                                                                                                                                                                      |

|   | Switching) under software control?                                                                                                                                                                                                                  |

|   | Q4.8: If the XRT94L43 has gone through an APS (Automatic Protection Switching) event, can the XRT94L43 device still monitor the state of the STS-12/STM-4 signal                                                                                    |

|   | that being received via the "Primary Receive STS-12/STM-4 PECL Interface" port? 74                                                                                                                                                                  |

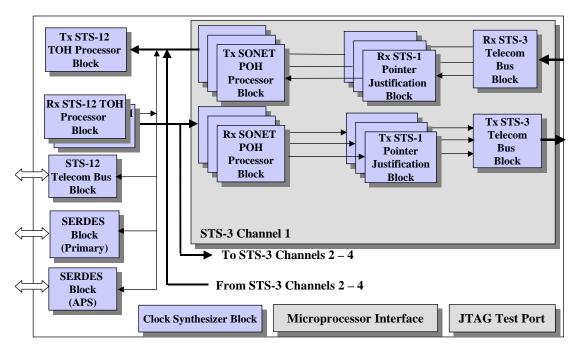

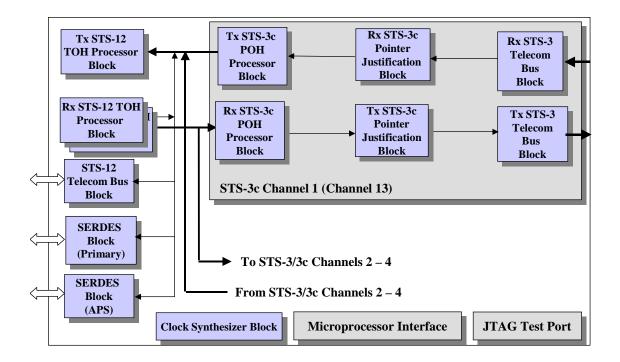

| n | 5: 4-Channel STS-3 to STS-12 Mapper-Related Questions                                                                                                                                                                                               |

| Ľ | Q5.1: How does one configure the XRT94L43 device to operate in the "4-Channel                                                                                                                                                                       |

|   | STS-3 to STS-12 Mapper" Mode?                                                                                                                                                                                                                       |

|   | Q5:2: If the XRT94L43 device is configured to operate in the "4-Channel STS-3 to                                                                                                                                                                    |

|   | STS-12 Mapper" Mode, can it be configured to support STS-3c signals?                                                                                                                                                                                |

## Frequently Asked Questions regarding the XRT94L43FAQ

Channel DS3/E3/STS-1 to STS-12/STM-4 Mapper IC

#### Preliminary

August 15, 2006

| Q5.3: Does the XRT94L43 device handle/process STS-3 and STS-3c signals differently                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Q6: Transmit and Receive SONET POH Processor Block Related Questions                                                                                        |

| Q6.1: Does the Transmit SONET POH Processor Block contain any "Transmit Path                                                                                |

| Trace Message" Buffer?                                                                                                                                      |

| Q6.2: Does the Receive SONET POH Processor Block contain any "Receive Path                                                                                  |

| Trace Message" Buffer?                                                                                                                                      |

| Q6.3: Can the user configure the Transmit SONET POH Processor block to                                                                                      |

| automatically transmit the AIS-P indicator, in the "outbound" STS-1 SPE data-stream                                                                         |

| (via the outbound STS-12 signal) anytime the corresponding Receive STS-1 TOH                                                                                |

| Processor block detects certain defect conditions?                                                                                                          |

| Q6.4: Does the XRT94L43 device permit the user to control the values of certain POH                                                                         |

| bytes, within the 12 outbound STS-1 signals (that are ultimately mapped into an STS-                                                                        |

| 12 signal), via on-chip registers?                                                                                                                          |

| Q6.5: Does the XRT94L43 device permit the user to monitor the values of certain                                                                             |

| POH bytes by software (via on-chip registers), within the 12 inbound STS-1 signals                                                                          |

| that have been de-mapped from STS-12?                                                                                                                       |

| Q6.6: Does the XRT94L43 device permit one to arbitrarily fix the Pointer Values of                                                                          |

| each STS-1/VC-3 within the outbound STS-12 data-stream?                                                                                                     |

| Q7: STS-12/STM-4 Telecom Bus Related Questions                                                                                                              |

| Q7.1: What signals exist within the Transmit STS-12/STM-4 Telecom Bus Interface                                                                             |

| block?                                                                                                                                                      |

| Q7.2: What signals exist within the Receive STS-12/STM-4 Telecom Bus Interface block?                                                                       |

|                                                                                                                                                             |

| Q7.3: Can the user configure the Transmit STS-12/STM-4 Telecom Bus Interface block to align its transmit of an STS-12 or STM-4 frame, with an external 8kHz |

| signal?                                                                                                                                                     |

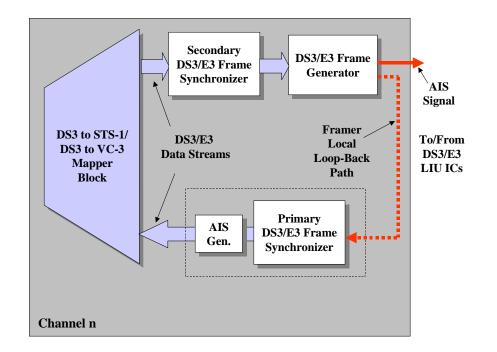

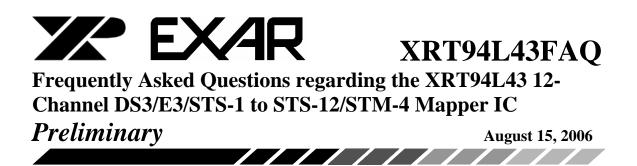

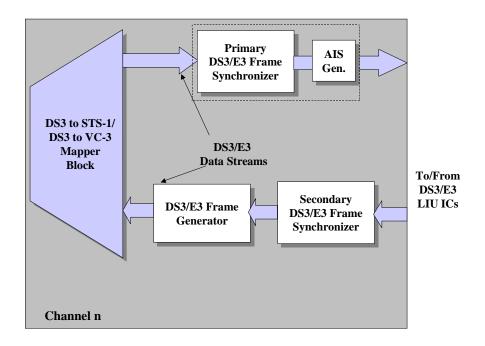

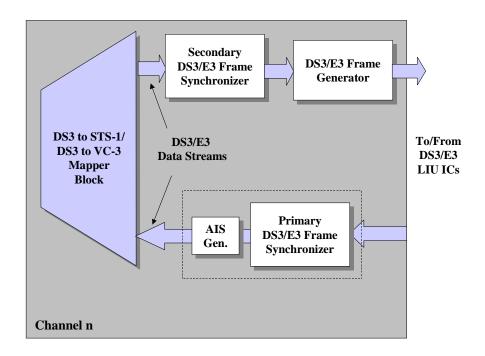

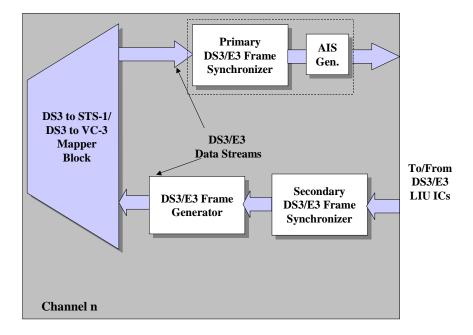

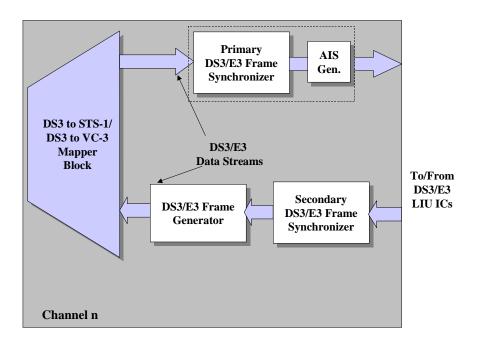

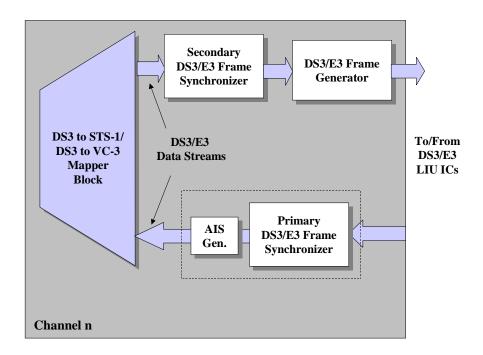

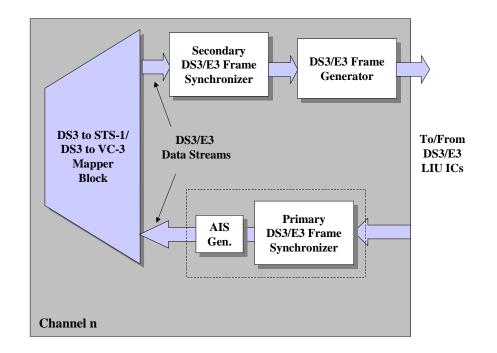

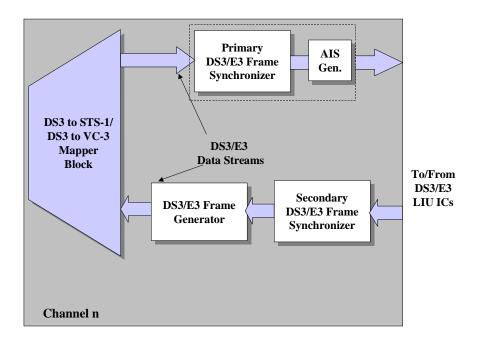

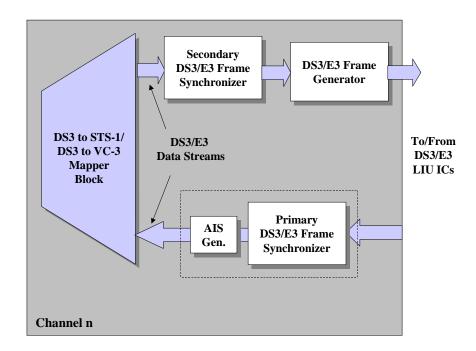

| Q8: DS3/E3 Framer Block Related Questions                                                                                                                   |

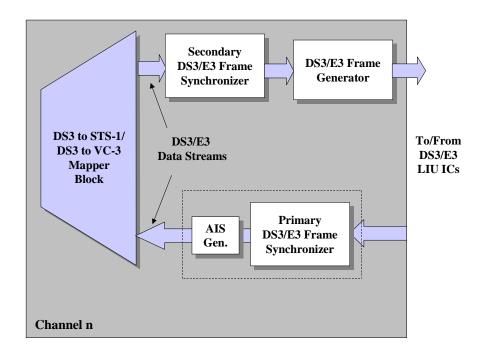

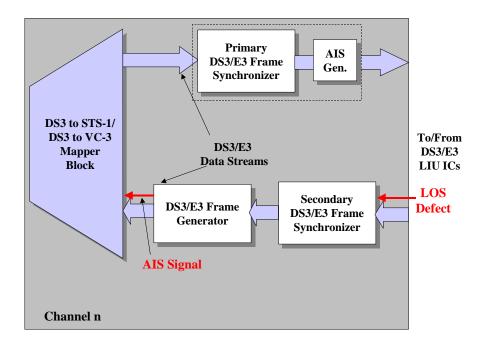

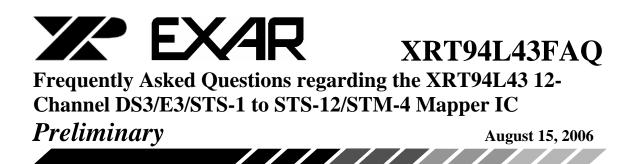

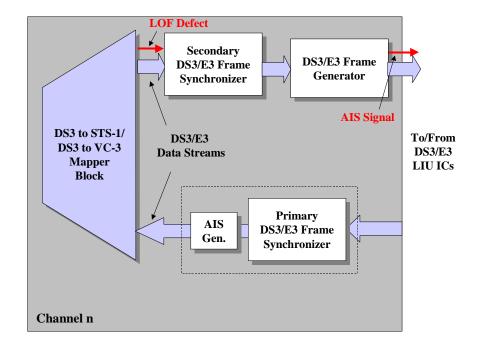

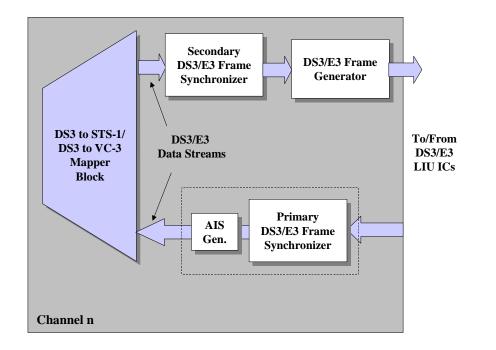

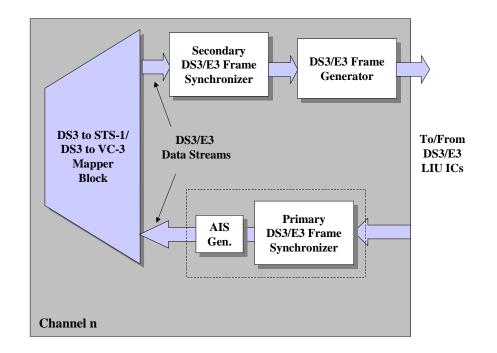

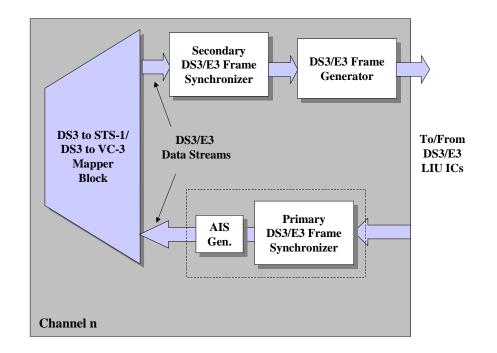

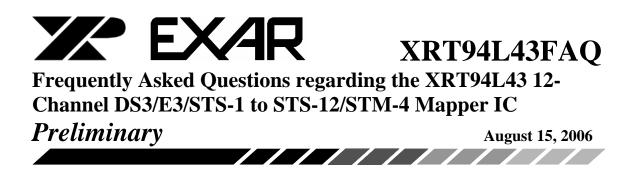

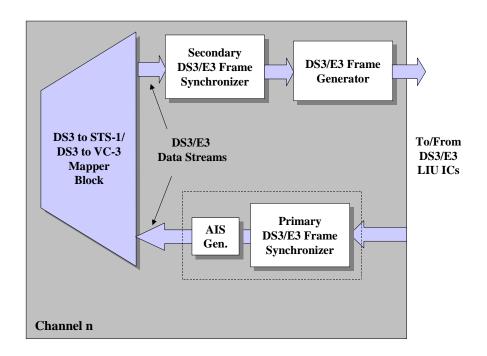

| Q8.1: What sub-blocks exist within the DS3/E3 Framer block (within each channel of                                                                          |

| the XRT94L43 device)?                                                                                                                                       |

| Q8.2: What framing formats are supported by the DS3/E3 Framer blocks?                                                                                       |

| Q8.3: What are the differences between the Primary and Secondary Frame                                                                                      |

| Synchronizer blocks?                                                                                                                                        |

| Q8.4: Which Frame Generator/Frame Synchronizer Configurations are recommended                                                                               |

| for handling normal DS3/E3 traffic?                                                                                                                         |

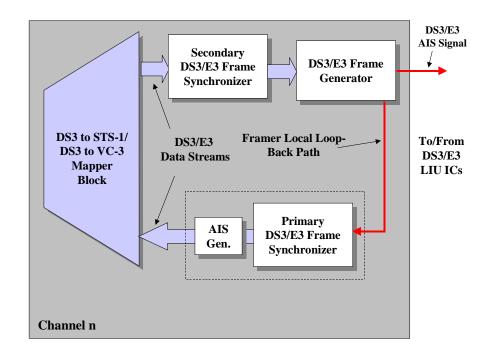

| Q8.5: What steps does one need to execute in order to (1) configure the DS3/E3                                                                              |

| Framer block into a Framer Local Loop-back Mode, and (2) to enable the PRBS                                                                                 |

| Pattern Generator and Receiver for diagnostic operation? 118                                                                                                |

| Q8.6: What steps does one need to execute in order to (1) configure the XRT94L43                                                                            |

| device into the Local Path Loop-back Mode, (2) to enable the PRBS Pattern Generator                                                                         |

##

Frequently Asked Questions regarding the XRT94L43 12-Channel DS3/E3/STS-1 to STS-12/STM-4 Mapper IC

#### **Preliminary**

August 15, 2006

XRT94L43FAQ

and Receiver (within the DS3/E3 Framer block), and (3) to check for proper data Q8.7: What steps does one need to execute in order to (1) configure the XRT94L43 device into the Local Transport Loop-back Mode, (2) to enable the PRBS Pattern Generator and Receive (within the DS3/E3 Framer block), and (3) to check for proper Q8.8: Can the DS3/E3 Framer blocks handle a Channelized DS3 data-stream that is of Q8.9: If the user has selected "Frame Generator/Frame Synchronizer Configuration # 23" can the user configure the DS3/E3 Framer block to automatically transmit the DS3/E3 AIS indicator towards the Mapper block, in response to a defect being Q8.10: If the user has selected "Frame Generator/Frame Synchronizer Configuration # 23" can the user configure the corresponding Transmit SONET POH Processor block to automatically transmit the PDI-P indicator, in response to a defect being detected in Q8.11: If the user has selected "Frame Generator/Frame Synchronizer Configuration # 23" can the user configure the DS3/E3 block to automatically transmit the DS3/E3 AIS indicator (in the Egress Direction) in response to a defect being detected in the Egress Q8.12: If the user has selected "Frame Generator/Frame Synchronizer Configuration # 23" can the user configure the DS3/E3 block to automatically transmit the DS3/E3 AIS indicator (in the Egress Direction) in response to the corresponding Receive SONET Q8.13: If the user has selected "Frame Generator/Frame Synchronizer Configuration # 28" can the user configure the DS3/E3 Framer block to automatically transmit the DS3/E3 AIS Indicator towards the Mapper block, in response to a defect being Q8.14: If the user has selected "Frame Generator/Frame Synchronizer Configuration # 28" can the user configure the corresponding Transmit SONET POH Processor block to automatically transmit the PDI-P indicator, in response to a defect being detected in Q8.15: If the user has selected "Frame Generator/Frame Synchronizer Configuration # 28" can the user configure the DS3/E3 block to automatically transmit the DS3/E3 AIS indicator (in the Egress Direction) in response to a defect being detected in the Egress DS3/E3 signal (coming from the DS3/E3 Mapper block)? ...... 191 Q8.16: If the user has selected "Frame Generator/Frame Synchronizer Configuration # 28" can the user configure the DS3/E3 block to automatically transmit the DS3/E3 AIS indicator (in the Egress Direction) in response to the corresponding Receive SONET

## X EXAR

Frequently Asked Questions regarding the XRT94L43 12-Channel DS3/E3/STS-1 to STS-12/STM-4 Mapper IC

#### **Preliminary**

August 15, 2006

XRT94L43FAQ

| Q8.17: Does the Primary Synchronizer block (within the DS3/E3 Framer block)                                                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| contain Performance Monitor registers that accumulate LCV (Line Code Violations)                                                                      |

| and EXZs (Excessive Zeros)?                                                                                                                           |

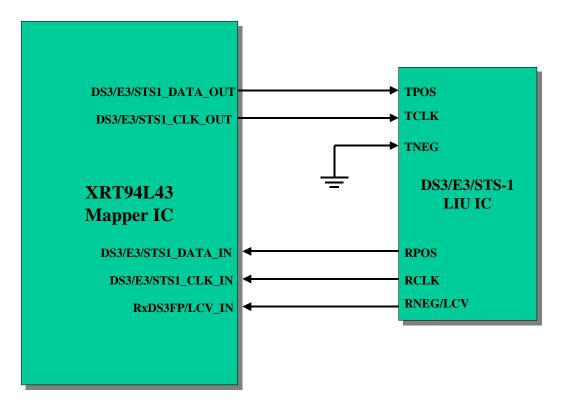

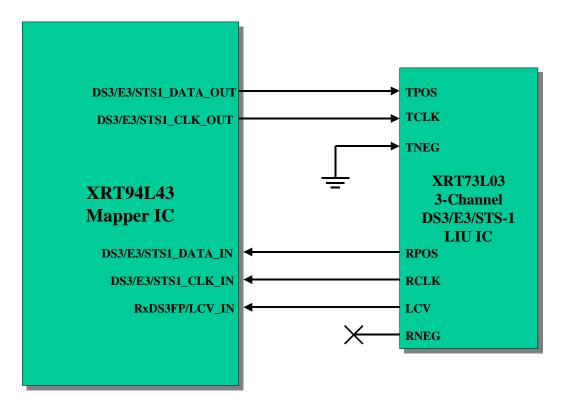

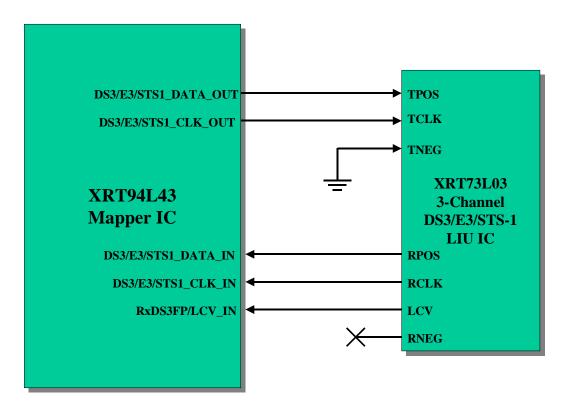

| Q8.18: How should one interface a DS3/E3/STS-1 LIU IC to the XRT94L43 device in                                                                       |

| order to ensure that the Primary Synchronizer block (within the DS3/E3 Framer block)                                                                  |

| will properly increment the "LCV" or "EXZ" Performance Monitor Registers,                                                                             |

| whenever it detects LCVs or EXZs in the incoming DS3 or E3 line signal?                                                                               |

| Q8.19: Can the XRT94L43 device be configured to pass an E3, ITU-T G.751 Signal                                                                        |

| through the DS3/E3 Framer block (in both the Ingress and Egress Direction) when                                                                       |

| mapping this E3 signal into, or de-mapping this E3 signal from SDH without altering                                                                   |

| the E3 Overhead Bits?                                                                                                                                 |

| Q8.20 Can the XRT94L43 device be configured to pass an E3, ITU-T G.832 Signal                                                                         |

| through the DS3/E3 Framer block (in both the Ingress and Egress Direction) when                                                                       |

| mapping this E3 signal into, or de-mapping this E3 signal from SDH without altering                                                                   |

| the E3 Overhead bytes?                                                                                                                                |

| Q8.21: Can one configure the XRT94L43 device to handle E3-rate data in an                                                                             |

| unframed manner?                                                                                                                                      |

| Q8.22: Can one configure the XRT94L43 device to handle DS3-rate data in an                                                                            |

| unframed manner?                                                                                                                                      |

| <b>Q9:</b> Transmit and Receive STS-1 TOH/POH Processor Block Related Questions 216                                                                   |

| Q9.1: Can the XRT94L43 device be configured to process STS-1 signals with VT-                                                                         |

| mapped SPEs?                                                                                                                                          |

| Q9.2: Does the XRT94L43 device permit the user to control the values of certain TOH                                                                   |

| bytes, within the 12 outbound STS-1 signals, via on-chip registers?                                                                                   |

| Q9.3: Does the XRT94L43 device permit the user to monitor the values of certain                                                                       |

| TOH bytes by software (via on-chip registers), within the 12 inbound STS-1 signals,                                                                   |

| via on-chip registers?                                                                                                                                |

| Q9.4: What procedure must one execute in order to read out the contents of the most                                                                   |

| recently received Section Trace Message, within a given STS-1 signal, that is being                                                                   |

| received by a given Receive STS-1 TOH Processor block?                                                                                                |

| Q9.5: What procedure must one execute in order to read out the contents of the most                                                                   |

| recently received Path Trace Message, within a given STS-1 signal, that is being                                                                      |

| received by a given Receive STS-1 POH Processor block?                                                                                                |

| Q9.6: Does the XRT94L43 device permit the user to control the values of certain POH                                                                   |

| bytes, within the 12 outbound STS-1 signals, via on-chip registers?                                                                                   |

| Q9.7: Does the XRT94L43 device permit the user to monitor the values of certain                                                                       |

| POH bytes by software (via on-chip registers), within the 12 inbound STS-1 signal that have been received via the Receive STS-1 POH Processor blocks? |

| HAVE DEED IELEIVEN VIA HE NELEIVE $\Delta 1 \Delta - 1 \text{ FULL FLOCESSOF DIOCKS}$ (                                                               |

|                                                                                                                                                       |

| Q10: Power Consumption/Thermal-Related Questions       240         Q10.1: What is the Power Consumption of the XRT94L43 device?       240             |

## X EXAR

XRT94L43FAQ

Frequently Asked Questions regarding the XRT94L43 12-Channel DS3/E3/STS-1 to STS-12/STM-4 Mapper IC

#### **Preliminary**

| Q10.2: What is the estimated Die Temperature of the XRT94L43 device?                | /1 |

|-------------------------------------------------------------------------------------|----|

| Q10.2: What is the estimated Die Temperature of the XRT94L43 device?                | 71 |

|                                                                                     | 43 |

| Q11: DS3/E3/STS-1 LIU Interface Related Questions                                   |    |

| Q11.1: Can the DS3/E3 LIU Interface of the XRT94L43 device be configured to         |    |

| operate in the Single-Rail Mode?                                                    |    |

| Q11.2: Can the STS-1/STM-0 LIU Interface of the XRT94L43 device be configured       | L  |

| to operate in the Dual-Rail Mode?                                                   | 49 |

| Q11.3: Suppose that one wishes to operate the DS3/E3 Framer block in Frame          |    |

| Generator/Frame Synchronizer Configuration # 28, and if this user also wishes to    |    |

| interface four (4) XRT73L03 devices to the XRT94L43 device. What configuration      |    |

| steps should one do to make this work properly?                                     | 50 |

| Q11.4: Suppose that one wishes to interface four (4) XRT73L03 devices to the        |    |

| XRT94L43 device, and to support the transmission of STS-1/STM-0 data. What          |    |

| configuration steps should one do to make this work properly?                       |    |

| Q12: SDH Related Questions                                                          | /3 |

| Q12.1: Can the XRT94L43 device be configured to support both SDH/AU-3 and           | 72 |

| SDH/TUG-3 Mapping?                                                                  | 13 |

| Mapping Mode, is there a way to read out the contents of the VC-4 POH bytes, within | n  |

| the incoming STM-4 data-stream via the Microprocessor Interface?                    |    |

| Q13: Transmit and Receive STS-12 TOH Processor Block Related Questions              |    |

| Q13.1: Does the XRT94L43 device permit the user to control the values of certain    | 02 |

| TOH bytes, within the outbound STS-12 signal, via on-chip registers?                | 82 |

| Q13.2: Does the XRT94L43 device permit the user to monitor the values of certain    | 02 |

| TOH bytes by software (via on-chip registers) within the inbound STS-12 signal, via |    |

| on-chip registers?                                                                  |    |

| Q13.3: Can the user configure the Transmit STS-12/STM-4 PECL Interface block to     |    |

| align its transmit of an STS-12 or STM-4 frame, with an external 8kHz signal? 2     |    |

#### Q1: On-Chip Jitter Attenuator-related Questions.

#### Q1.1: What is APS Recovery Time of the XRT94L43 device?

A1.1: In all cases, the APS Recovery Time (of the XRT94L43 device) was measured to be less than 2ms (which is well within the 50ms APS Completion Time requirements, per Section 5.3.3.3 of Telcordia GR-253-CORE).

**NOTE:** If the user wishes to obtain more information on our approach to measuring the APS Recovery Time of the XRT94L43 device, then he/she should refer to "Test Report – Automatic Protection Switching (APS) Recovery Time Testing with the XRT94L43 12-Channel DS3/E3/STS-1 to STS-12 Mapper IC – Revision C Silicon"

## Q1.2: What Frequency Accuracy is required at the REFCLK34 (pin P23), REFCLK45 (pin P25) or REFCLK51 (pin P24) input pins?

A1.2: These input pins are used as a "Reference Clock" by the "Jitter Attenuator/Clock Smoother" PLLs within the De-Map Direction. The user is advised to apply a  $34.368MHz \pm 20$ ppm signal to the REFCLK34 input pin, a  $44.736MHz \pm 20$ ppm signal to the REFCLK45 input pin or a  $51.84MHz \pm 20$ ppm signal to the REFCLK51 input pin. This recommendation (of using clock signals with an accuracy of  $\pm 20$ ppm) is made in order to reduce or minimize the "LOCK" time of the "Clock Smoother PLL" within the XRT94L43 IC.

However, for minimal performance, the Clock Smoother PLL requires that the user supply a line-rate clock  $\pm$  750ppm. However, the use of a more accurate clock signal (at each of these pins) will improve chip performance (e.g., reduce the "LOCK" time).

## Q1.3: If one only intends to support DS3 and STS-1/STM-0 signals via the XRT94L43 device, is it still necessary to supply a 34.368MHz clock signal to the REFCLK34 input pin?

A1.3: No, in this case the user should simply tie the REFCLK34 input pin to GND. In addition to tying the REFCLK34 input pin to GND, the user should also write the value "[1, 1]" into Bits 6 and 5 (SDH JA Freq\_Sel[1:0]) within the "Mode Control Register-Byte 0" as depicted below.

|                      |                    |                                     | 0                                                               | ,                                                                                              |                                                                                                                               | ,                                                                                                        |

|----------------------|--------------------|-------------------------------------|-----------------------------------------------------------------|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| Bit 6                | Bit 5              | Bit 4                               | Bit 3                                                           | Bit 2                                                                                          | Bit 1                                                                                                                         | Bit 0                                                                                                    |

| SDH JA Freq_Sel[1:0] |                    | Unused                              | AU3_3/                                                          | AU3_2/                                                                                         | AU3_1/                                                                                                                        | AU3_0/                                                                                                   |

|                      |                    |                                     | TUG_3*                                                          | TUG_2*                                                                                         | TUG_1*                                                                                                                        | TUG_0*                                                                                                   |

|                      |                    |                                     |                                                                 |                                                                                                |                                                                                                                               |                                                                                                          |

|                      |                    |                                     |                                                                 |                                                                                                |                                                                                                                               |                                                                                                          |

|                      |                    |                                     |                                                                 |                                                                                                |                                                                                                                               |                                                                                                          |

| R/W                  | R/W                | R/O                                 | R/W                                                             | R/W                                                                                            | R/W                                                                                                                           | R/W                                                                                                      |

| 1                    | 1                  | 0                                   | 0                                                               | 0                                                                                              | 0                                                                                                                             | 0                                                                                                        |

|                      | Bit 6<br>SDH JA Fr | Bit 6 Bit 5<br>SDH JA Freq_Sel[1:0] | Bit 6     Bit 5     Bit 4       SDH JA Freq_Sel[1:0]     Unused | Bit 6     Bit 5     Bit 4     Bit 3       SDH JA Freq_Sel[1:0]     Unused     AU3_3/<br>TUG_3* | Bit 6     Bit 5     Bit 4     Bit 3     Bit 2       SDH JA Freq_Sel[1:0]     Unused     AU3_3/<br>TUG_3*     AU3_2/<br>TUG_2* | Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1SDH JA Freq_Sel[1:0]UnusedAU3_3/<br>TUG_3*AU3_2/<br>TUG_2*AU3_1/<br>TUG_1* |

#### Mode Control Register – Byte 0 (Indirect Address = 0x00, 0x1B; Direct Address = 0x011B)

This setting will configure the Jitter Attenuators within the XRT94L43 device to handle DS3 and STS-1 signals.

The user will still need to supply a 44.736MHz  $\pm$ 20ppm signal to the REFCLK45 input pin; if he/she wishes to map and de-map DS3 signals into/from an STS-12/STM-4 signal. Likewise, the user will also still need to supply a 51.84MHz  $\pm$  20ppm signal to the REFCLK51 input pin; if he/she wishes to map and de-map STS-1/STM-0 signals into/from an STS-12/STM-4 signal.

## Q1.4: If one only intends to support DS3 and E3 signals via the XRT94L43 device, is it still necessary to supply a 51.84MHz clock signal to the REFCLK51 input pin?

A1.4: No, in this case, the user should simply tie the REFCLK51 input pin to GND. IN addition to tying the REFCLK51 input pin to GND, the user should also write the value "[0, X]" into Bits 6 and 5 (SDH JA Freq\_Sel[1:0]) within the "Mode Control Register – Byte 0" as depicted below.

|          |                      |       | eee maar ess | 01100,0112 | ) = == = = = = = = = = = = = = = = = = | ebb eneril | /      |

|----------|----------------------|-------|--------------|------------|----------------------------------------|------------|--------|

| Bit 7    | Bit 6                | Bit 5 | Bit 4        | Bit 3      | Bit 2                                  | Bit 1      | Bit 0  |

| APS      | SDH JA Freq_Sel[1:0] |       | Unused       | AU3_3/     | AU3_2/                                 | AU3_1/     | AU3_0/ |

| Recovery |                      |       |              | TUG_3*     | TUG_2*                                 | TUG_1*     | TUG_0* |

| Time     |                      |       |              |            |                                        |            |        |

| Mode     |                      |       |              |            |                                        |            |        |

| Disable  |                      |       |              |            |                                        |            |        |

| R/W      | R/W                  | R/W   | R/O          | R/W        | R/W                                    | R/W        | R/W    |

| 0        | 0                    | Х     | 0            | 0          | 0                                      | 0          | 0      |

#### Mode Control Register – Byte 0 (Indirect Address = 0x00, 0x1B; Direct Address = 0x011B)

This setting will configure the Jitter Attenuators within the XRT94L43 device to handle DS3 and E3 signals.

The user will still need to supply a 44.736MHz ±20ppm signal to the REFCLK45 input pin; if he/she wishes to map and de-map DS3 signals into/from an STS-12/STM-4 signal. Likewise, the user will also still need to supply a 34.368MHz ±20ppm signal to the REFCLK34 input pin; if he/she wishes to map and de-map E3 signals into/from an STM-4 signal.

#### Q1.5: Are the DS3 signals, which are extracted out of the XRT94L43 device (from SONET) capable of complying with the Category 1 Intrinsic Jitter Requirements per Telcordia GR-253-CORE and ANSI T1.105.03-1994?

A1.5: Yes, each of the 12 channels, within the XRT94L43 device, contains a DS3/E3 Jitter Attenuator block, which operates in the "De-Map" direction. These Jitter Attenuator blocks actually consists of a very narrow-band PLL and a FIFO. The results of extensive testing (per Section 5.6 within Telcordia GR-253-CORE) indicate that each of these 12 channels complies with these Intrinsic Jitter Requirements.

**NOTE:** A detailed write up on how well the XRT94L43 complies with these Intrinsic Jitter Requirements, can be found in the report entitled "Test Report: Telcordia GR-253-CORE Category 1 Intrinsic Jitter Requirements (for DS3 Applications) Test Results for the XRT94L43 device (Revision C Silicon)".

## Q1.6: What does one need to do in order to configure the XRT94L43 Device to support "Daisy-Chain" Testing?

A1.6: First of all, the basic concept behind Daisy-Chain Testing is that one can "snake" a given DS3 or E3 signal through each of the 12-channels (in a Daisy-Chain Manner). This "DS3" or "E3" signal could either by applied directly to one of the Ingress Direction Ports of the chip (via Test Equipment) or it could be applied to the XRT94L43 device via the Receive STS-12/STM-4 Port" (of the chip).

If the user wishes to configure the XRT94L43 device to support "Daisy-Chain" operation, then he/she needs to set the "on-chip" Jitter Attenuators to the correct bandwidth (for this operation). The user can accomplish this by setting the "Jitter Attenuator BW[2:0]" bit-fields (Bits 7 through 5, within the "Mode Control Register – Byte 1) to either [0, 1, 1] or [1, 0, 0] as depicted below.

| Bit 7                     | Bit 6 | Bit 5 | Bit 4  | Bit 3                 | Bit 2 | Bit 1 | Bit 0 |

|---------------------------|-------|-------|--------|-----------------------|-------|-------|-------|

| Jitter Attenuator BW[2:0] |       |       | Unused | STS-1 Access SEL[1:0] |       |       |       |

| R/W                       | R/W   | R/W   | R/O    | R/O                   | R/O   | R/W   | R/W   |

| 0                         | 1     | 1     | 0      | 0                     | 0     | 0     | 0     |

| 1                         | 0     | 0     |        |                       |       |       |       |

Mode Control Register – Byte 1 (Indirect = 0x00, 0x1A, Direct Address = 0x011A)

#### NOTES:

- 1. Setting Jitter Attenuator BW[2:0] to "[0, 1, 1]" configures the Jitter Attenuator Bandwidth to be 3.15Hz.

- 2. Setting Jitter Attenuator BW[2:0] to "[1, 0, 0]" configures the Jitter Attenuator Bandwidth to be 11.8Hz.

- 3. This setting applies to all 12 Jitter Attenuator blocks within the chip.

- 4. For normal applications (e.g., in which the customer is required to comply with either the Category I Intrinsic Jitter Requirements (per Telcordia GR-253-CORE) or the Intrinsic Jitter requirements (per ITU-T G.783), then we recommend that the user set these bit-fields to "[0, 0, 0]".

#### Q2: Clock Synthesizer Block-Related Questions.

## Q2.1: What Frequency Accuracy is required at the REFCLK input pin (pin R1)?

A2.1: The "REFCLK" input pin functions as a clock source for the on-chip 622.08MHz clock synthesizer block. The XRT94L43 device contains an on-chip clock synthesizer that can be configured to generate a 622.08MHz clock signal from either of the following clock frequencies.

- 77.76MHz

- 51.84MHz

- 19.44MHz

- 12.96MHz

#### NOTES:

- 1. In many SONET/SDH systems, the user is required to operate with a line-rate  $\pm$  4.6ppm clock signal. If the user is required to generate and transmit data at a rate of 622.08MHz  $\pm$  4.6ppm, then the user will need to make sure that the abovementioned clock source signals (which are supplied to the REFCLK input pin) are of equal frequency accuracy ( $\pm$ 4.6ppm).

- Similarly, if the user is only required to generate and transmit data at a rate of 622.08MHz ± 20ppm, then the user will need to make sure that the abovementioned clock source signals (which are supplied to the REFCLK input pin) are of equal frequency accuracy (±20ppm).

## Q2.2: How does one configure the Clock Synthesizer block to synthesize a 77.76MHz clock signal, when provided with a 19.44MHz clock signal?

A2.2: The user accomplishes this by (1) supplying a 19.44MHz clock signal to the "REFCLK" input pin, and then, (2) writing the value 0x60 into the "Interface Control Register – Byte 2" as depicted below.

## Interface Control Register – Byte 2 (Indirect Address = 0x00, 0x31; Direct Address = 0x0131)

| Bit 7 | Bit 6   | Bit 5 | Bit 4   | Bit 3  | Bit 2 | Bit 1 | Bit 0 |  |

|-------|---------|-------|---------|--------|-------|-------|-------|--|

| REFFR | EQ[1:0] | Synth | Ext 622 | Unused |       |       |       |  |

|       |         | Clock |         |        |       |       |       |  |

| R/W   | R/W     | R/W   | R/W     | R/O    | R/O   | R/O   | R/O   |  |

| 0     | 1       | 1     | 0       | 0      | 0     | 0     | 0     |  |

This setting configures the Clock Synthesizer block to externally accept a 19.44MHz clock signal via the REFCLK (pin R4) pin, and internally synthesize a 77.76MHz clock signal from this signal.

# **The answer of the states of t**

## Q2.3 How does one configure the XRT94L43 Device to use the 77.76MHz clock signal (which is supplied to the REFCLK input pin) as a timing reference?

A2.3: The user accomplishes this by doing the following.

STEP 1 – Supply a 77.76MHz clock signal to the REFCLK input pin (pin R4).

STEP 2 – Write the value "0xC0" into the "Interface Control Register – Byte 2" as depicted below.

Interface Control Register – Byte 2 (Indirect Address = 0x00, 0x31; Direct Address = 0x0131)

| Bit 7 | Bit 6   | Bit 5 | Bit 4   | Bit 3  | Bit 2 | Bit 1 | Bit 0 |  |

|-------|---------|-------|---------|--------|-------|-------|-------|--|

| REFFR | EQ[1:0] | Synth | Ext 622 | Unused |       |       |       |  |

|       |         | Clock |         |        |       |       |       |  |

| R/W   | R/W     | R/W   | R/W     | R/O    | R/O   | R/O   | R/O   |  |

| 1     | 1       | 0     | 0       | 0      | 0     | 0     | 0     |  |

In this configuration setting, the internal circuitry (within the XRT94L43 device) is being directly clocked by the 77.76MHz clock signal that is being provided to the REFCLK input pin. The Clock Synthesizer is "by-passed".

**NOTE:** If the user intends to transmit the outbound STS-12/STM-4 data via the "Transmit STS-12/STM-4 PECL Interface", then the user will need to enable the clock synthesizer block by also setting Bit 5 (Synth Clock) within the "Interface Control Register – Byte 2" to "1" as depicted below.

Interface Control Register – Byte 2 (Indirect Address = 0x00, 0x31; Direct Address = 0x0131)

| Bit 7 | Bit 6   | Bit 5 | Bit 4   | Bit 3  | Bit 2 | Bit 1 | Bit 0 |  |

|-------|---------|-------|---------|--------|-------|-------|-------|--|

| REFFR | EQ[1:0] | Synth | Ext 622 | Unused |       |       |       |  |

|       |         | Clock |         |        |       |       |       |  |

| R/W   | R/W     | R/W   | R/W     | R/O    | R/O   | R/O   | R/O   |  |

| 1     | 1       | 1     | 0       | 0      | 0     | 0     | 0     |  |

The user MUST enable the Clock Synthesizer block in order to internally synthesize the 622.08MHz clock necessary for the Transmit STS-12/STM-4 PECL Interface to operate.

#### Q3: General Configuration-Related Questions.

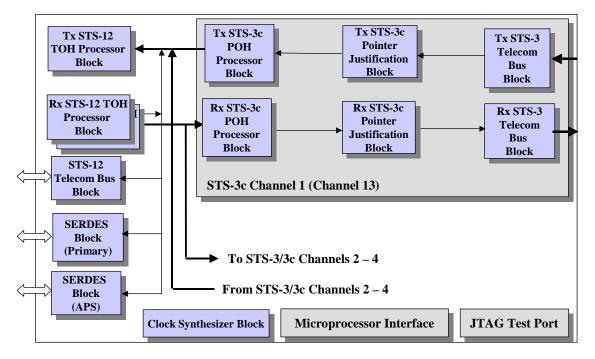

## Q3.1 Is it permissible to configure the XRT94L43 device to support combinations of the STS-3 Telecom Bus Interface and the DS3/E3/STS-1 Interface?

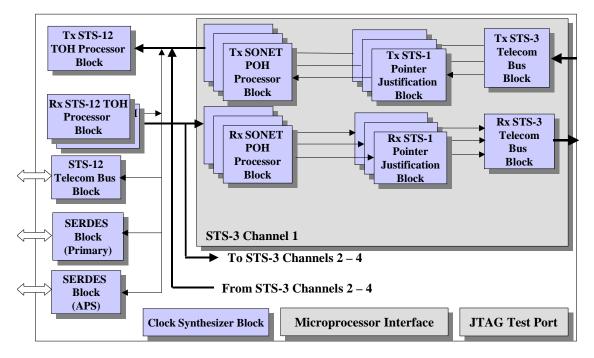

A3.1: Yes, the XRT94L43 device can be thought of as consisting of 4 "STS-3 Blocks". Each of these "STS-3 Blocks" can be configured to function as either an STS-3 Telecom Bus interface or 3 DS3/E3/STS-1 interfaces. Each of these four (4) "STS-3 Blocks" can be configured independent of each other.

The user can configure a given "STS-3 Block" to operate in either the "STS-3 Telecom Bus" or in the DS3/E3/STS-1 Mode by writing the appropriate value into Bit 7 (STS-3 # N TB ON), within each of the following registers.

- Interface Control Register Byte 3 STS-3 Telecom Bus 3 (Indirect Address = 0x00, 0x38; Direct Address = 0x0138)

- Interface Control Register Byte 2 STS-3 Telecom Bus 2 (Indirect Address = 0x00, 0x39; Direct Address = 0x0139)

- Interface Control Register Byte 1 STS-3 Telecom Bus 1 (Indirect Address = 0x00, 0x3A; Direct Address = 0x013A)

- Interface Control Register Byte 0 STS-3 Telecom Bus 0 (Indirect Address = 0x00, 0x3B; Direct Address = 0x013B)

The bit-format of each of these registers is identical, and is presented below for completeness.

| 0400, 04 | 0x00, 0x50 - 0x5D, Direct indiress - 0x0150 - 0x015D) |        |        |       |        |        |         |  |  |  |  |

|----------|-------------------------------------------------------|--------|--------|-------|--------|--------|---------|--|--|--|--|

| Bit 7    | Bit 6                                                 | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0   |  |  |  |  |

| STS-3    | TB BUS                                                | Unused | STS TB | STS-3 | STS-3  | STS-3  | STS-3   |  |  |  |  |

| TB # N   | Disable                                               |        | Parity | TB J1 | TB     | TB     | Rephase |  |  |  |  |

| ON       |                                                       |        | Туре   | ONLY  | Parity | Parity |         |  |  |  |  |

|          |                                                       |        |        |       | Odd    | Enable |         |  |  |  |  |

| R/W      | R/W                                                   | R/0    | R/W    | R/W   | R/W    | R/W    | R/W     |  |  |  |  |

| X        | X                                                     | Х      | Х      | Х     | Х      | Х      | Х       |  |  |  |  |

## Interface Control Register – Byte N – STS-3 Telecom Bus 3 (Indirect Address = 0x00, 0x38 – 0x3B; Direct Address = 0x0138 – 0x013B)

## X EXAR

Frequently Asked Questions regarding the XRT94L43 12-Channel DS3/E3/STS-1 to STS-12/STM-4 Mapper IC

#### **Preliminary**

August 15, 2006

XRT94L43FAQ

Setting Bit 7 (STS-3 TB # N ON) to "1" configures "STS-3 Block" Number "N" to operate in the "STS-3 Telecom Bus" Mode. Conversely, setting this bit-field to "0" configures "STS-3 Block" Number "N" to operate in the DS3/E3/STS-1 Mode.

## The Mapping between the DS3/E3/STS-1 Channels and the STS-3 Telecom Bus Interface Channels

As indicated in the text above, if the user enables a certain STS-3 Telecom Bus, then certain DS3/E3/STS-1 Channels will be disabled. The following table presents the relationship between each of the STS-3 Telecom Bus Interfaces and the corresponding DS3/E3/STS-1 Channels.

| I CICCOIII DUS III                  |                                     |

|-------------------------------------|-------------------------------------|

| STS-3 Telecom Bus Interface Channel | Corresponding DS3/E3/STS-1 Channels |

| 0                                   | 0, 4, 8                             |

| 1                                   | 1, 5, 9                             |

| 2                                   | 2, 6, 10                            |

| 3                                   | 3, 7, 11                            |

## Table 3-1, The Mapping between the DS3/E3/STS-1 Channels and the STS-3Telecom Bus Interface Channel

## Q3.2 How does one configure a given channel to operate in the DS3/E3 Framer Mode?

The XRT94L43 device can be configured to operate in two basic modes.

- STS-3 to STS-12 Mapper Mode

- STS-1/DS3/E3 to STS-12/STM-4 Mapper Mode.

If one configures the XRT94L43 device to operate in the "STS-3 to STS-12 Mapper" Mode, then many input/output pins will be configured to function as "19.44MHz Telecom Bus Interface" pins. Conversely, if one configures the XRT94L43 device to operate in the "STS-1/DS3/E3 to STS-12/STM-4 Mapper" Mode, then many input/output pins will be configured to function as Clock and Data Interfaces to external DS3/E3/STS-1 LIU devices.

Unfortunately, these Telecom Bus pins and the "LIU Interface" pins are one in the same. Therefore, if the user wishes to operate the XRT94L43 device in the "STS-1/DS3/E3 to STS-12 Mapper" Mode, then he/she must disable the STS-3 Telecom Bus Interface blocks.

This is accomplished by executing the following four steps.

#### **STEP 1 – Disable Telecom Bus # 3**

This is accomplished by setting Bit 7 (STS-3 TB # 3 ON) to "0", as illustrated below.

| <br>Address = 0 | x0138) |        |         |         |          |         |         |

|-----------------|--------|--------|---------|---------|----------|---------|---------|

| Bit 7           | Bit 6  | Bit 5  | Bit 4   | Bit 3   | Bit 2    | Bit 1   | Bit 0   |

| STS-3 TB        | TB BUS | Unused | STS TB  | STS3 TB | STS-3 TB | STS3 TB | STS3    |

| #3              | DIS    |        | PAR_TYP | J1 ONLY | PAR      | PAR ENB | REPHASE |

| ON              |        |        |         |         | ODD      |         |         |

| R/W             | R/W    | R/W    | R/W     | R/W     | R/W      | R/W     | R/W     |

| 0               | 0      | 0      | 0       | 0       | 0        | 0       | 0       |

Interface Control Register – Byte 3 – STS-3 Telecom Bus 3 (Indirect Address = 0x00, 0x38; Direct Address = 0x0138)

#### **STEP 2 – Disable Telecom Bus # 2**

This is accomplished by setting Bit 7 (STS-3 TB # 2 ON) to "0", as illustrated below.

#### Interface Control Register – Byte 2 – STS-3 Telecom Bus 2 (Indirect Address = 0x00, 0x39; Direct Address = 0x0139)

| ]  | Bit 7  | Bit 6  | Bit 5  | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   |

|----|--------|--------|--------|---------|---------|---------|---------|---------|

| ST | S-3 TB | TB BUS | Unused | STS TB  | STS3 TB | STS3 TB | STS3 TB | STS3    |

|    | #2     | DIS    |        | PAR_TYP | J1 ONLY | PAR     | PAR ENB | REPHASE |

|    | ON     |        |        |         |         | ODD     |         |         |

| ]  | R/W    | R/W    | R/W    | R/W     | R/W     | R/W     | R/W     | R/W     |

|    | 0      | 0      | 0      | 0       | 0       | 0       | 0       | 0       |

#### **STEP 3 – Disable Telecom Bus # 1**

This is accomplished by setting Bit 7 (STS-3 TB # 1 ON) to "0", as illustrated below.

Interface Control Register – Byte 1 – STS-3 Telecom Bus 1 (Indirect Address = 0x00, 0x3A; Direct Address = 0x013A)

| Bit 7    | Bit 6  | Bit 5  | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   |

|----------|--------|--------|---------|---------|---------|---------|---------|

| STS-3 TB | TB BUS | Unused | STS TB  | STS3 TB | STS3 TB | STS3 TB | STS3    |

| # 1      | DIS    |        | PAR_TYP | J1 ONLY | PAR     | PAR ENB | REPHASE |

| ON       |        |        |         |         | ODD     |         |         |

| R/W      | R/W    | R/W    | R/W     | R/W     | R/W     | R/W     | R/W     |

| 0        | 0      | 0      | 0       | 0       | 0       | 0       | 0       |

#### STEP 4 – Disable Telecom Bus # 0

This is accomplished by setting Bit 7 (STS-3 TB # 0 ON) to "0", as illustrated below.

Interface Control Register – Byte 0 – STS-3 Telecom Bus 0 (Indirect Address = 0x00, 0x3B; Direct Address = 0x013B)

| Bit 7    | Bit 6  | Bit 5  | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   |

|----------|--------|--------|---------|---------|---------|---------|---------|

| STS-3 TB | TB BUS | Unused | STS3/12 | STS3/12 | STS3/12 | STS3/12 | STS3/12 |

| # 0      | DIS    |        | TB      | TB J1   | TB PAR  | TB PAR  | REPHASE |

| ON       |        |        | PAR_TYP | ONLY    | ODD     | ENB     | STS-3   |

| R/W      | R/W    | R/W    | R/W     | R/W     | R/W     | R/W     | R/W     |

| 0        | 0      | 0      | 0       | 0       | 0       | 0       | 0       |

If the user executes each of these four (4) steps, then all of the STS-3 Telecom Bus pins will now be configured to function as "DS3/E3/STS-1 LIU Interface" pins.

# **The answer of the states of t**

#### STEP 5 - Configuring the DS3/E3/STS-1 Channel Blocks to support DS3/E3 Applications

If the user wishes to configure a given channel, to operate in the DS3/E3 Mode, then he/she can accomplish this by setting both Bits 1 (Receive STS-1 Enable) and 0 (Transmit STS-1 Enable), within the corresponding Mapper Control Registers (Byte 2) to "0" as illustrated below.

| Bit 7     | Bit 6     | Bit 5     | Bit 4  | Bit 3  | Bit 2    | Bit 1   | Bit 0  |

|-----------|-----------|-----------|--------|--------|----------|---------|--------|

| STS-1 OH  | STS-1     | STS-1     | STS-1  | Loop-  | POH Pass | Ingress | Egress |

| Pass Thru | Remote    | Local     | TOH    | Timing | Thru     | STS-1   | STS-1  |

|           | Loop-back | Loop-back | Insert |        |          | Enable  | Enable |

| R/W       | R/W       | R/W       | R/W    | R/W    | R/W      | R/W     | R/W    |

| 0         | 0         | 0         | 0      | 0      | 0        | 0       | 0      |

#### Mapper Control Register – Byte 2 (Indirect Address = 0xN6, 0x01; Direct Address = 0xN701)

#### NOTES:

- a. Setting Bits 1 (Receive STS-1 Enable) and Bits 0 (Transmit STS-1 Enable) to "1" would configure the Channel to operate in the STS-1 Mode.

- b. The Indirect Address Location of the "Mapper Control Register Byte 2" is 0xN6, 0x01; where "N" denotes the channel number and can range from "1" to "C".

## Q3.3 How does one configure a given channel to operate in the STS-1 Mode?

The XRT94L43 device can be configured to operate in two basic modes.

- STS-3 to STS-12 Mapper Mode

- STS-1/DS3/E3 to STS-12/STM-4 Mapper Mode.

If one configures the XRT94L43 device to operate in the "STS-3 to STS-12 Mapper" Mode, then many input/output pins will be configured to function as "19.44MHz Telecom Bus Interface" pins. Conversely, if one configures the XRT94L43 device to operate in the "STS-1/DS3/E3 to STS-12/STM-4 Mapper" Mode, then many input/output pins will be configured to function as Clock and Data Interfaces to external DS3/E3/STS-1 LIU devices.

Unfortunately, these Telecom Bus pins and the "LIU Interface" pins are one in the same. Therefore, if the user wishes to operate the XRT94L43 device in the "STS-1/DS3/E3 to STS-12 Mapper" Mode, then he/she must disable the STS-3 Telecom Bus Interface blocks.

This is accomplished by executing the following four steps.

#### **STEP 1 – Disable Telecom Bus # 3**

This is accomplished by setting Bit 7 (STS-3 TB # 3 ON) to "0", as illustrated below.

| <br>Address = 0 | x0138) |        |         |         |          |         |         |

|-----------------|--------|--------|---------|---------|----------|---------|---------|

| Bit 7           | Bit 6  | Bit 5  | Bit 4   | Bit 3   | Bit 2    | Bit 1   | Bit 0   |

| STS-3 TB        | TB BUS | Unused | STS TB  | STS3 TB | STS-3 TB | STS3 TB | STS3    |

| #3              | DIS    |        | PAR_TYP | J1 ONLY | PAR      | PAR ENB | REPHASE |

| ON              |        |        |         |         | ODD      |         |         |

| R/W             | R/W    | R/W    | R/W     | R/W     | R/W      | R/W     | R/W     |

| 0               | 0      | 0      | 0       | 0       | 0        | 0       | 0       |

Interface Control Register – Byte 3 – STS-3 Telecom Bus 3 (Indirect Address = 0x00, 0x38; Direct Address = 0x0138)

#### STEP 2 – Disable Telecom Bus # 2

This is accomplished by setting Bit 7 (STS-3 TB # 2 ON) to "0", as illustrated below.

#### Interface Control Register – Byte 2 – STS-3 Telecom Bus 2 (Indirect Address = 0x00, 0x39; Direct Address = 0x0139)

| ]  | Bit 7  | Bit 6  | Bit 5  | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   |

|----|--------|--------|--------|---------|---------|---------|---------|---------|

| ST | S-3 TB | TB BUS | Unused | STS TB  | STS3 TB | STS3 TB | STS3 TB | STS3    |

|    | #2     | DIS    |        | PAR_TYP | J1 ONLY | PAR     | PAR ENB | REPHASE |

|    | ON     |        |        |         |         | ODD     |         |         |

| ]  | R/W    | R/W    | R/W    | R/W     | R/W     | R/W     | R/W     | R/W     |

|    | 0      | 0      | 0      | 0       | 0       | 0       | 0       | 0       |

#### **STEP 3 – Disable Telecom Bus # 1**

This is accomplished by setting Bit 7 (STS-3 TB # 1 ON) to "0", as illustrated below.

Interface Control Register – Byte 1 – STS-3 Telecom Bus 1 (Indirect Address = 0x00, 0x3A; Direct Address = 0x013A)

| Bit 7    | Bit 6  | Bit 5  | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   |

|----------|--------|--------|---------|---------|---------|---------|---------|

| STS-3 TB | TB BUS | Unused | STS TB  | STS3 TB | STS3 TB | STS3 TB | STS3    |

| # 1      | DIS    |        | PAR_TYP | J1 ONLY | PAR     | PAR ENB | REPHASE |

| ON       |        |        |         |         | ODD     |         |         |

| R/W      | R/W    | R/W    | R/W     | R/W     | R/W     | R/W     | R/W     |

| 0        | 0      | 0      | 0       | 0       | 0       | 0       | 0       |

#### **STEP 4 – Disable Telecom Bus # 0**

This is accomplished by setting Bit 7 (STS-3 TB # 0 ON) to "0", as illustrated below.

Interface Control Register – Byte 0 – STS-3 Telecom Bus 0 (Indirect Address = 0x00, 0x3B; Direct Address = 0x013B)

| Bit 7    | Bit 6  | Bit 5  | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   |

|----------|--------|--------|---------|---------|---------|---------|---------|

| STS-3 TB | TB BUS | Unused | STS3/12 | STS3/12 | STS3/12 | STS3/12 | STS3/12 |

| # 0      | DIS    |        | TB      | TB J1   | TB PAR  | TB PAR  | REPHASE |

| ON       |        |        | PAR_TYP | ONLY    | ODD     | ENB     | STS-3   |

| R/W      | R/W    | R/W    | R/W     | R/W     | R/W     | R/W     | R/W     |

| 0        | 0      | 0      | 0       | 0       | 0       | 0       | 0       |

If the user executes each of these four (4) steps, then all of the STS-3 Telecom Bus pins will now be configured to function as "DS3/E3/STS-1 LIU Interface" pins.

# **The answer of the state of the**

#### STEP 5 – Configure the Jitter Attenuator Block to handle STS-1 signals

Set Bits 6 and 5 (SDH JA Freq\_Sel[1:0]) to the value "[1, X]", as depicted below.

#### Mode Control Register – Byte 0 (Indirect Address = 0x00, 0x1B; Direct Address = 0x011B)

|          |                      |       |        | , .    | ,      |        | /      |

|----------|----------------------|-------|--------|--------|--------|--------|--------|

| Bit 7    | Bit 6                | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

| APS      | SDH JA Freq_Sel[1:0] |       | Unused | AU3_3/ | AU3_2/ | AU3_1/ | AU3_0/ |

| Recovery |                      |       |        | TUG_3* | TUG_2* | TUG_1* | TUG_0* |

| Time     |                      |       |        |        |        |        |        |

| Mode     |                      |       |        |        |        |        |        |

| Disable  |                      |       |        |        |        |        |        |

| R/W      | R/W                  | R/W   | R/O    | R/W    | R/W    | R/W    | R/W    |

| 0        | 1                    | Х     | 0      | 0      | 0      | 0      | 0      |

This setting will configure the Jitter Attenuator blocks to be able to handle an STS-1 signal.

**NOTE:** For most North American Applications, the user may wish to write the value "[1, 1]" into these bit-fields. This will configure the Jitter Attenuator blocks to handle both STS-1 and DS3 signals.

#### STEP 6 - Configuring the DS3/E3/STS-1 Channel Blocks to support STS-1 Applications

If the user wishes to configure a given channel, to operate in the STS-1 Mode, then he/she can accomplish this by setting both Bits 1 (Receive STS-1 Enable) and 0 (Transmit STS-1 Enable), within the corresponding Mapper Control Registers (Byte 2) to "1" as illustrated below.

| Mapper Co | Mapper Control Register – Byte 2 (Indirect Address = 0xNo, 0x01; Direct Address = 0xN/01) |           |        |        |          |         |        |  |  |  |  |  |

|-----------|-------------------------------------------------------------------------------------------|-----------|--------|--------|----------|---------|--------|--|--|--|--|--|

| Bit 7     | Bit 6                                                                                     | Bit 5     | Bit 4  | Bit 3  | Bit 2    | Bit 1   | Bit 0  |  |  |  |  |  |

| STS-1 OH  | STS-1                                                                                     | STS-1     | STS-1  | Loop-  | POH Pass | Ingress | Egress |  |  |  |  |  |

| Pass Thru | Remote                                                                                    | Local     | TOH    | Timing | Thru     | STS-1   | STS-1  |  |  |  |  |  |

|           | Loop-back                                                                                 | Loop-back | Insert |        |          | Enable  | Enable |  |  |  |  |  |

| R/W       | R/W                                                                                       | R/W       | R/W    | R/W    | R/W      | R/W     | R/W    |  |  |  |  |  |

| 0         | 0                                                                                         | 0         | 0      | 0      | 0        | 1       | 1      |  |  |  |  |  |

Mapper Control Register – Byte 2 (Indirect Address = 0xN6, 0x01; Direct Address = 0xN701)

#### **NOTES:**

- a. Setting Bits 1 (Receive STS-1 Enable) and 0 (Transmit STS-1 Enable) to "0" would configure the Channel to operate in the DS3/E3 Mode.

- b. The Indirect Address Location of the "Mapper Control Register Byte 2" is 0xN6, 0x01; where "N" denotes the channel number and can range from "1" to "C".

## Q3.4: What type of Loop-back Modes are available within the XRT94L43 device?

A3.4The XRT94L43 device supports all of the following loop-back modes.

- The Remote Line Loop-back Mode

- The Local Transport Loop-back Mode

- The Local Path Loop-back Mode

- STS-1 Local Loop-back Mode

- STS-1 Remote Loop-back Mode

- DS3/E3 Framer Local Loop-back Mode

- DS3/E3 Framer Remote Loop-back Mode

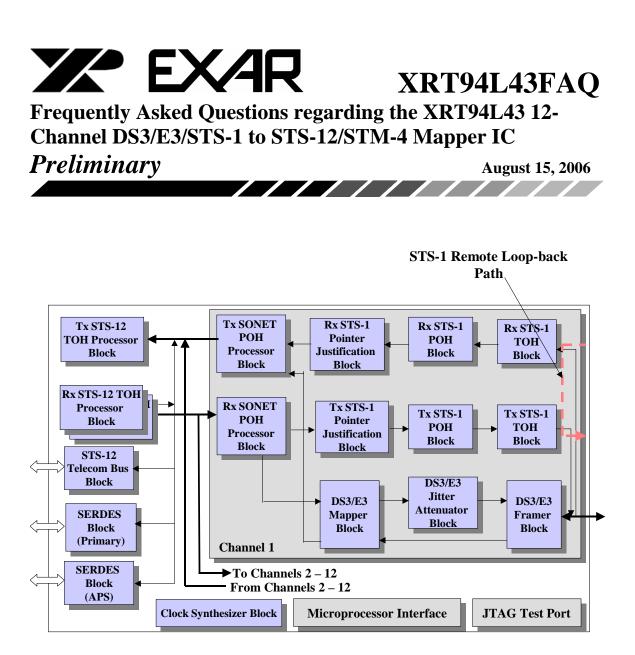

An illustration and description of each of these Loop-back Modes are presented below.

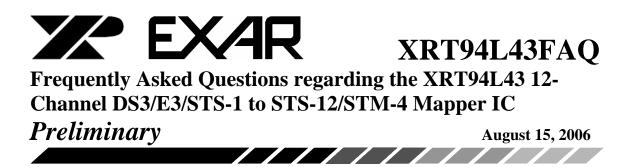

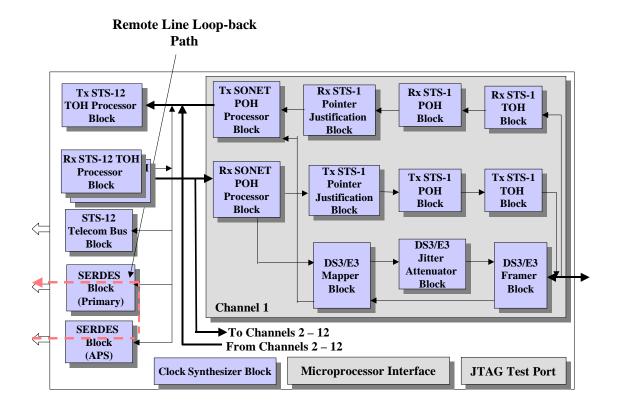

#### Remote Line Loop-back Mode

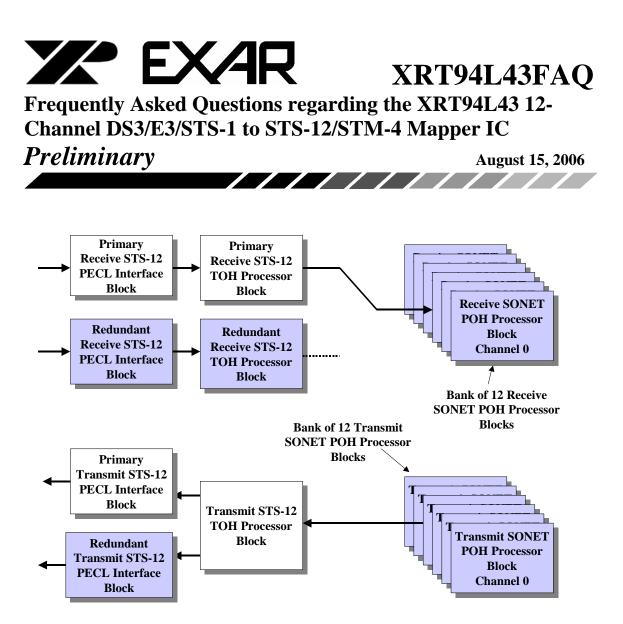

In this mode, all data, which is received by the "Receive STS-12/STM-4 PECL Interface" block will be routed to the "Transmit STS-12/STM-4 PECL Interface" block, as depicted below.

Figure 3-1, Illustration of the Remote Line Loop-back Mode

**NOTE:** In the Remote Line Loop-back Mode, the STS-12/STM-4 signal is not routed through any XRT94L43 Framer block circuitry.

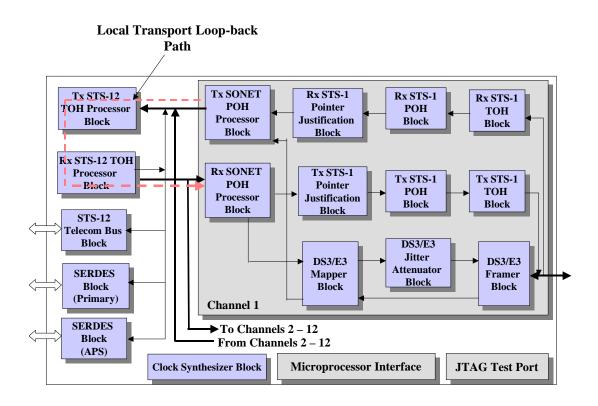

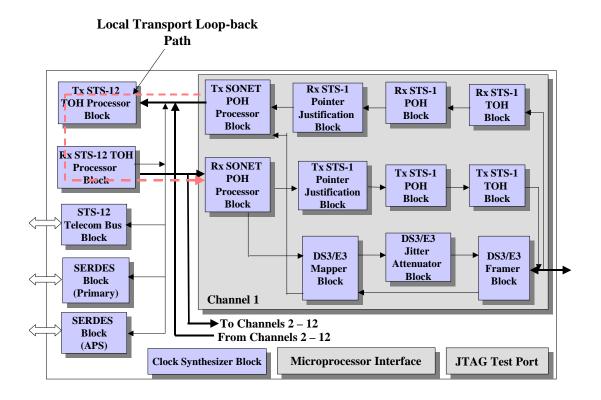

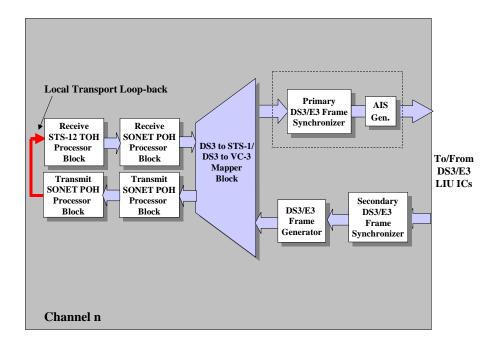

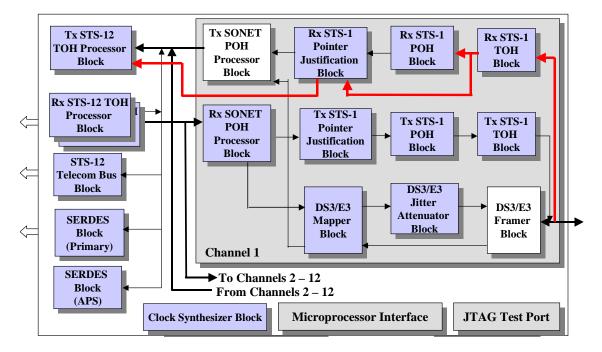

#### Local Transport Loop-back Mode

In this mode, all data, which is being output via the "Transmit STS-12 TOH Processor" block, will be internally routed to the "Receive STS-12 TOH Processor" block as depicted below.

Figure 3-2, Illustration of the Local Transport Loop-back Mode

**NOTE:** If the user configures the XRT94L43 device to operate in the "Local Transport Loop-back" Mode, then, in addition to "routing" the "Transmit Output STS-12 data back into the "Receive Path (as depicted in Figure 3-2), the Transmit Output STS-12 data is still output via either the "Transmit STS-12/STM-4 PECL Interface" or the "Transmit STS-12/STM-4 Telecom Bus Interface", depending upon user configuration.

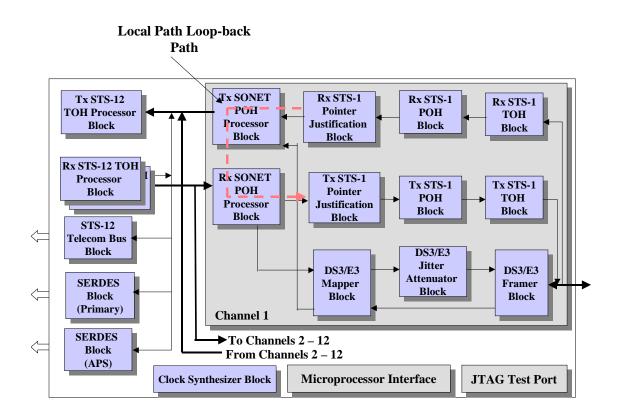

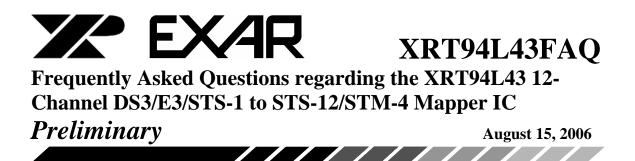

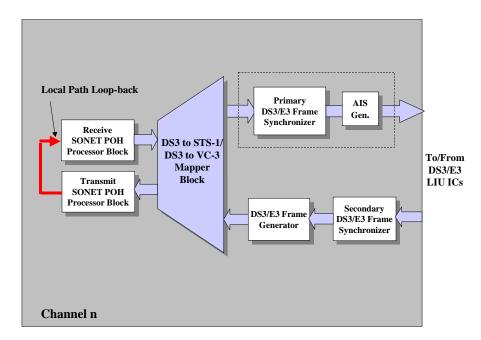

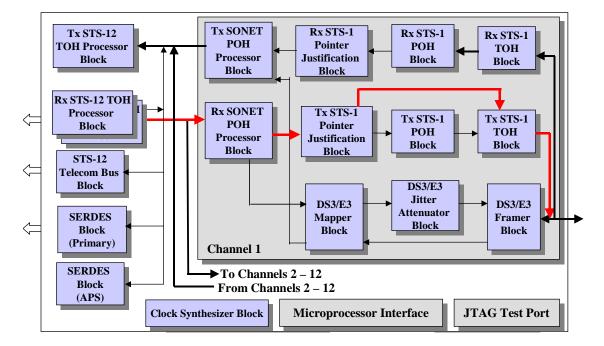

#### Local Path Loop-back Mode

In this mode, all data, which is being transmitted by the Transmit SONET POH Processor block will be internally routed back into the receive input of the Receive SONET POH Processor block.

**NOTE:** If the user invokes the "Local Path Loop-back" Mode, then this loop-back path will exist for all 12 channels, within the XRT94L43 device.

Figure 3-3, Illustration of the Local Path Loop-back Mode

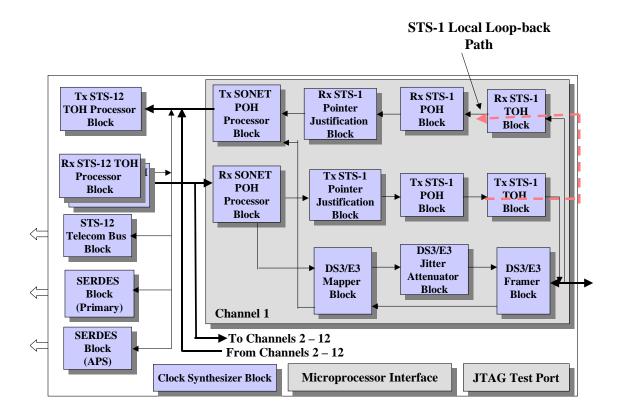

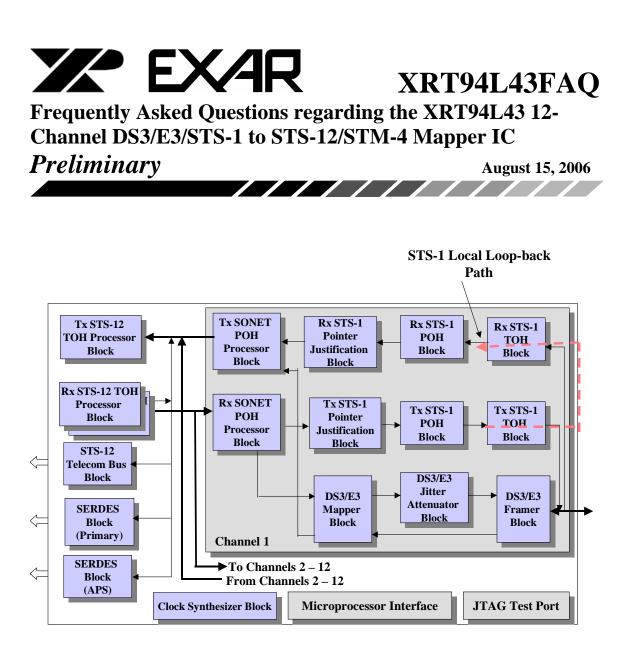

#### STS-1 Local Loop-back Mode

In this mode, all data that is being output via the "Transmit STS-1 TOH Processor" block will be internally routed to the "Receive STS-1 TOH Processor" block, as depicted below.

**NOTE:** This loop-back mode can be configured on a "per-channel" basis.

Figure 3-4, Illustration of the STS-1 Local Loop-back Mode

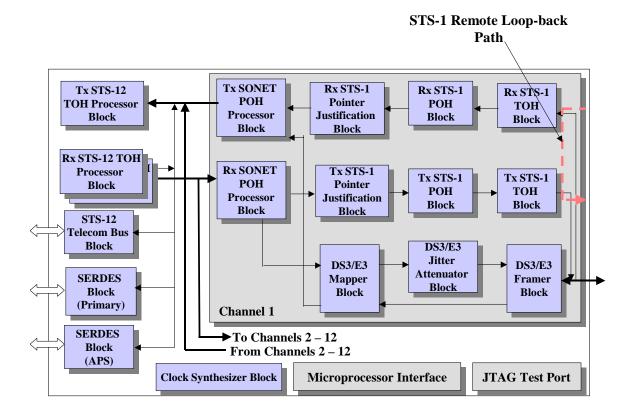

#### STS-1 Remote Loop-back Mode

In this mode, all data, which is received by a given channel (within the XRT94L43 device) at the Receive STS-1 Input will be internally routed to the Transmit STS-1 Output.

#### **NOTES:**

- 1. The STS-1 Remote Loop-back signal path is NOT routed through the Receive STS-1 TOH Processor and Transmit STS-1 TOH Processor blocks.

- 2. This loop-back mode can be configured on a "per-channel" basis.

Figure 3-5, Illustration of the STS-1 Remote Loop-back Mode

#### Q3.5: How does one configure the XRT94L43 device to operate in the "Remote Line Loop-back" Mode?

A3.5: The user accomplishes this by writing the value "0x01" into the "Loop-back Control Register – Byte 0" as depicted below.

| Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2          | Bit 1 | Bit 0 |  |  |

|-------|--------|-------|-------|-------|----------------|-------|-------|--|--|

|       | Unused |       |       |       | Loop-back[3:0] |       |       |  |  |

| R/O   | R/O    | R/O   | R/O   | R/W   | R/W            | R/W   | R/W   |  |  |

| 0     | 0      | 0     | 0     | 0     | 0              | 0     | 1     |  |  |

#### Loop-back Control Register – Byte 0 (Indirect Address = 0x00, 0x1F; Direct Address = 0x011F)

For completeness sake, an illustration of the XRT94L43 device, when configured to operate in the Remote Local Loop-back Mode is presented below in Figure 3-6.

Figure 3-6, Illustration of the XRT94L43 Device, when configured to operate in the Remote Line Loop-back Mode

#### Q3.6: How does one configure the XRT94L43 device to operate in the "Local Transport Loop-back" Mode?

A3.6: The user accomplishes this by executing the following steps.

### **STEP 1:** Disable the "Auto AIS-P Downstream upon the various STS-12 Defect conditions" feature.

The user can accomplish this by executing the following two sub-steps.

STEP 1a: Writing the value "0x00" into the "Receive STS-12 Transport – Auto AIS Control Register" as depicted below.

Receive STS-12 Transport – Auto AIS Control Register (Indirect Address = 0x04, 0x63; Direct Address = 0x0563)

| Bit 7    | Bit 6    | Bit 5    | Bit 4    | Bit 3      | Bit 2    | Bit 1    | Bit 0    |

|----------|----------|----------|----------|------------|----------|----------|----------|

| Transmit | Transmit | Transmit | Transmit | Transmit   | Transmit | Transmit | Transmit |

| AIS-P    | AIS-P    | AIS-P    | AIS-P    | AIS-P      | AIS-P    | AIS-P    | AIS-P    |

| (Down-   | (Down-   | (Down-   | (Down-   | (Down-     | (Down-   | (Down-   | (Down-   |

| stream)  | stream)  | stream)  | stream)  | stream)    | stream)  | stream)  | stream)  |

| Upon J0  | Upon J0  | Upon SF  | Upon SD  | upon Loss  | upon LOF | upon LOS | Enable   |

| Message  | Message  | -        | -        | of Optical | -        | -        |          |

| Unstable | Mismatch |          |          | Carrier    |          |          |          |

|          |          |          |          | AIS        |          |          |          |

| R/W      | R/W      | R/W      | R/W      | R/W        | R/W      | R/W      | R/W      |

| 0        | 0        | 0        | 0        | 0          | 0        | 0        | 0        |

**NOTE:** If the user executes this step, then he/she will prevent the Receive STS-12 TOH Processor block from automatically transmitting the AIS-P indicator, in the downstream direction (towards the twelve Receive SONET POH Processor blocks) should it (the Receive STS-12 TOH Processor block) declare any of the above-mentioned defect conditions while attempting to execute "Local-Transport" Loop-back.

STEP 1b: Writing the value "0x00" into the "Receive STS-12 Transport – Auto AIS (in Downstream STS-1s) Control Register, as depicted below.

Receive STS-12 Transport – Auto AIS (in Downstream STS-1s) Control Register (Indirect Address = 0x04, 0x6B; Direct Address = 0x056B)

| Bit 7  | Bit 6  | Bit 5      | Bit 4      | Bit 3      | Bit 2      | Bit 1  | Bit 0      |  |  |

|--------|--------|------------|------------|------------|------------|--------|------------|--|--|

| Unused | Unused | Transmit   | Transmit   | Transmit   | Transmit   | AIS-L  | Transmit   |  |  |

|        |        | AIS-P (via | AIS-P (via | AIS-P (via | AIS-P (via | Output | AIS-P (via |  |  |

|        |        | Downstream | Downstream | Downstream | Downstream | Enable | Downstream |  |  |

|        |        | STS-1s)    | STS-1s)    | STS-1s)    | STS-1s)    |        | STS-1s)    |  |  |

|        |        | upon LOS   | upon LOF   | upon SD    | upon SF    |        | Enable     |  |  |

| R/O    | R/O    | R/W        | R/W        | R/W        | R/W        | R/W    | R/W        |  |  |

| 0      | 0      | 0          | 0          | 0          | 0          | 0      | 0          |  |  |

**NOTE:** If the user executes this step, then he/she will prevent each of the twelve (12) Transmit STS-1 TOH Processor block from automatically transmitting the AIS-P indicator, in the downstream direction (towards the DS3/E3/STS-1 LIU Devices) should the Receive STS-12 TOH Processor block declare any of the above-mentioned defect conditions while attempting to execute "Local-Transport" Loop-back.

## STEP 2 – Configure the XRT94L43 device to operate in the Local-Transport Loopback Mode.

The user accomplishes this by writing the value "0x02" into the "Loop-back Control Register – Byte 0" as depicted below.

| 200p and |        | 2,000 | (111011 000 1100 | 11000 | •mii , 2 m •••• |       |       |  |  |

|----------|--------|-------|------------------|-------|-----------------|-------|-------|--|--|

| Bit 7    | Bit 6  | Bit 5 | Bit 4            | Bit 3 | Bit 2           | Bit 1 | Bit 0 |  |  |

|          | Unused |       |                  |       | Loop-back[3:0]  |       |       |  |  |

| R/O      | R/O    | R/O   | R/O              | R/W   | R/W             | R/W   | R/W   |  |  |

| 0        | 0      | 0     | 0                | 0     | 0               | 1     | 0     |  |  |

Loop-back Control Register – Byte 0 (Indirect Address = 0x00, 0x1F; Direct Address = 0x011F)

For completeness sake, an illustration of the XRT94L43 device, when configured to operate in the Local Transport Loop-back Mode is presented below in Figure 3-7.

Figure 3-7, Illustration of the XRT94L43 device when configured to operate in the "Local Transport Loop-back" Mode

## Q3.7: How does one configure the XRT94L43 device to operate in the "Local Path Loop-back" Mode?

A3.7: The user accomplishes this by executing the following steps.

### **STEP 1:** Disable the "Auto AIS-P Downstream upon the various STS-12 Defect Conditions" features.

The user can accomplish this by executing the following two sub-steps.

STEP 1a. Writing the value "0x00" into the "Receive STS-12 Transport – Auto AIS Control Register" as depicted below.

Receive STS-12 Transport – Auto AIS Control Register (Indirect Address = 0x04, 0x63; Direct Address = 0x0563)

| Bit 7    | Bit 6    | Bit 5    | Bit 4    | Bit 3      | Bit 2    | Bit 1    | Bit 0    |

|----------|----------|----------|----------|------------|----------|----------|----------|

| Transmit | Transmit | Transmit | Transmit | Transmit   | Transmit | Transmit | Transmit |

| AIS-P    | AIS-P    | AIS-P    | AIS-P    | AIS-P      | AIS-P    | AIS-P    | AIS-P    |

| (Down-   | (Down-   | (Down-   | (Down-   | (Down-     | (Down-   | (Down-   | (Down-   |

| stream)  | stream)  | stream)  | stream)  | stream)    | stream)  | stream)  | stream)  |

| Upon J0  | Upon J0  | Upon SF  | Upon SD  | upon Loss  | upon LOF | upon LOS | Enable   |

| Message  | Message  | -        | -        | of Optical | _        | -        |          |

| Unstable | Mismatch |          |          | Carrier    |          |          |          |

|          |          |          |          | AIS        |          |          |          |

| R/W      | R/W      | R/W      | R/W      | R/W        | R/W      | R/W      | R/W      |

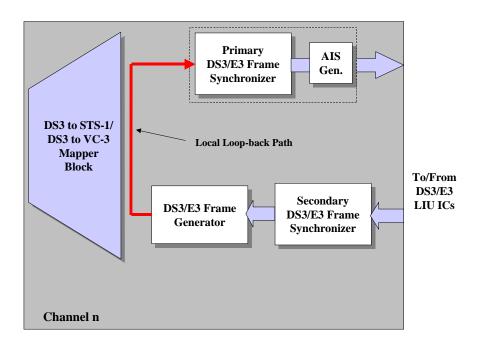

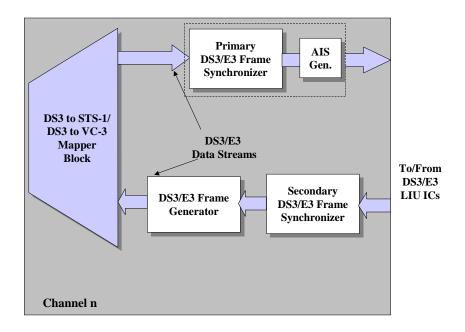

| 0        | 0        | 0        | 0        | 0          | 0        | 0        | 0        |